[C2] Exploring Power Attack Protection of Resource Constrained Encryption Engines using Integrated Low-Drop-Out Regulators

Abstract

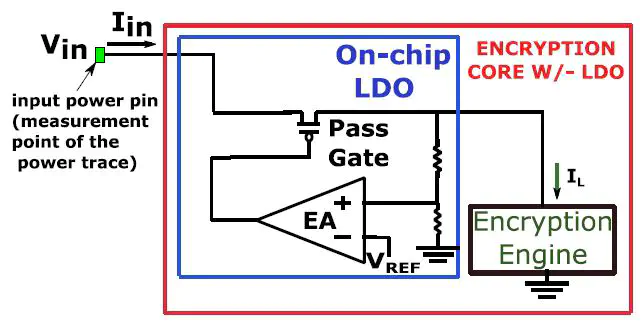

The power attack protection of encryption engines often comes at the expense of area, power, and/or performance overheads making the design of a low-power and compact but secure encryption engine challenging. This paper explores the feasibility of using an on-chip low dropout regulator (LDO) as a countermeasure to power attack of lowpower and compact encryption engine. We design an area minimized implementation of Advanced Encryption Standard (AES) using predictive 45nm node and show that lightweight implementations are more susceptible to power attack. Using behavioral modeling, we show that an on-chip LDO can enhance power attack resistance of this compact AES engine; however, the tradeoff between LDO performance and power attack protection is essential. Our analysis shows that LDO can increase power attack resistance of the compact AES by >800X with marginal area (1.4%) and power (5%) overheads.