[C46] An Energy Efficient Sorting Architecture with Cell-Gating for Top-K Sorting on FPGA

Abstract

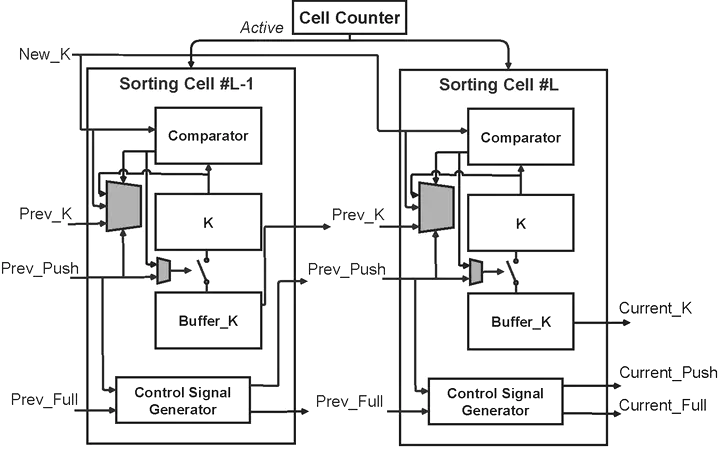

Top-K Sorting is a widely used technique for selecting the largest or smallest numbers from input elements. In this paper, we present an efficient low-power and flexible top-K sorting architecture with cell gating on field-programmable gate arrays (FPGAs). Our architecture consists of a data filter unit, cell counter, and L-cascaded sorting cells, where the filter unit allows users to select the user-defined data values to sort, the cell counter allows cell gating by counting the number of working cells, and the sorting cells allow sorting with low power and flexible K length with cell gating. The proposed sorting cells update incoming data continuously. In addition, cell gating is introduced to increase the flexibility of top-K length and energy efficiency by turning cells on and off. Our implementation achieves remarkable results with a power consumption of only 0.3W with L=128 and 200MHz on a Xilinx XCKU115 FPGA. Overall, our work contributes to advancing the state of the art in efficient and flexible K sorting on FPGAs.