[J7] Energy Efficient and Side-Channel Secure Cryptographic Hardware for IoT-edge Nodes

Abstract

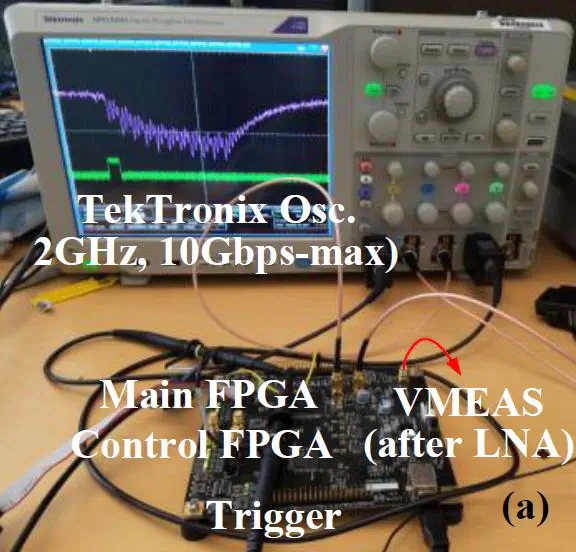

Design of ultra-lightweight but secure encryption engine is a key challenge for Internet-of-Things (IoT) edge devices. This paper explores the system level design space for an ultra-low power image sensor node for secure communication and proposes an optimized datapath architecture for 128-bit SIMON (SIMON128), a lightweight block cipher, for minimal performance, power and area overheads with increased level of side-channel security. Various datapath architectures for SIMON are explored for simultaneously increasing energy-efficiency and resistance to power based side-channel analysis (PSCA) attacks. Alternative datapath architectures are implemented on ASIC (15nm CMOS) and FPGA (Spartan-6, 45nm) to perform power, performance and area (PPA) analysis. We show that, although a bit-serial datapath minimizes area and power, a round unrolled datapath provides 80× higher energy-efficiency and 143× higher performance, compared to the baseline bitserial design. Moreover, the PSCA measurements performed using Sakura-G board with Spartan-6 FPGA, demonstrate that a 6-round unrolled datapath improves minimum-traces-to-disclosure (MTD) for correlation power analysis (CPA) by at least 384× over baseline bitserial design with no successful CPA even with 500,000 measurements. Finally, application to the image-sensor node demonstrates that optimized unrolled SIMON128 can provide equivalent performance to AES128 at lower area, higher energy efficiency and improved side channel security.